# **FPGA Based Pulse Width Modulation**

## P. Meenatchi Sundaram

Lecturer, ECE Department, VSVN Polytechnic College, Virudhunagar.

#### Abstract:

By controlling the voltage applied to different devices, the speed, heat and many parameters can be controlled. There are many methods to control the voltage and one among them is the Pulse Width Modulation technique. The duty cycle ischanged using Pulse Width Modulation. Pulse Width Modulated output can be got by different Circuits. Here, the Pulse Width Modulation block has a register, counter, comparator and RS Latch. The blocks are synthesized using VHDL in QUARTUS-II Integral Development Environment, simulated and downloaded in the Altera FPGA board. The on-time can be changed by changing the register value, the off-time by the counter value. The PWM waveform output is simulated using Modelsim software. Then PWM wave form can beverified by changing the intensity of LED in the FPGA board. In this project, the speed of a DC motor is controlled using the PWM technique. L293D Motor d. In the future, this PWM technique can be used for impedance matching of MPTT to extract maximum power from the Solar Panel.

## **Introduction:**

Pulse width modulation reduces the average power delivered by an electrical signal by converting the signal into discrete parts. In the PWM technique, the signal's energy is distributed through a series of pulses rather than a continuously varying (analogue) signal.

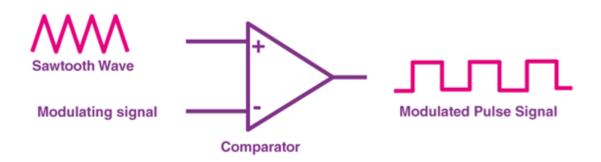

A pulse width modulating signal is generated using a comparator. The modulating signal forms one part of the input to the comparator, while the non-sinusoidal wave or sawtooth wave forms the other part of the input. The comparator compares two signals and generates a PWM signal as its output waveform.

#### Important Parameters associated with PWM signal:

#### **Duty Cycle of PWM:**

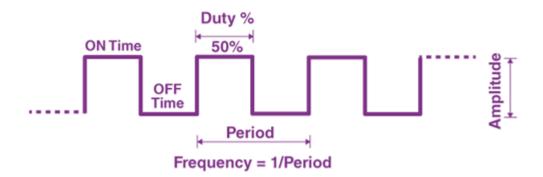

As we know, a PWM signal stays "ON" for a given time and stays "OFF" for a certain time. The percentage of time for which the signal remains "ON" is known as the duty cycle. If the signal is always "ON," then the signal must have a 100 % duty cycle. The formula to calculate the duty cycle is given as follows:

$$DutyCycle = \frac{TurnOnTime}{TurnOnTime + TurnOffTime}$$

The average value of the voltage depends on the duty cycle. As a result, the average value can be varied by controlling the width of the "ON" of a pulse.

#### **Frequency of PWM:**

The frequency of PWM determines how fast a PWM completes a period. The frequency of a pulse is shown in the figure above.

The frequency of PWM can be calculated as follows:

Frequency = 1/Time Period Time Period = On Time + OFF time

Output Voltage of PWM signal

The output voltage of the PWM signal will be the percentage of the duty cycle. For example, for a 100% duty cycle, if the operating voltage is 5V then the output voltage will also be 5V. If the duty cycle is 50%, then the output voltage will be 2.5V.

Types of Pulse Width Modulation Technique

There are three conventional types of pulse width modulation technique and they are named as follows:

- **Trail Edge Modulation** In this technique, the signal's lead edge is modulated, and the trailing edge is kept fixed.

- Lead Edge Modulation In this technique, the signal's lead edge is fixed, and the trailing edge is modulated.

- **Pulse Centre Two Edge Modulation** In this technique, the pulse centre is fixed and both edges of the pulse are modulated.

## **Block Diagram of Pulse Width Modulation :**

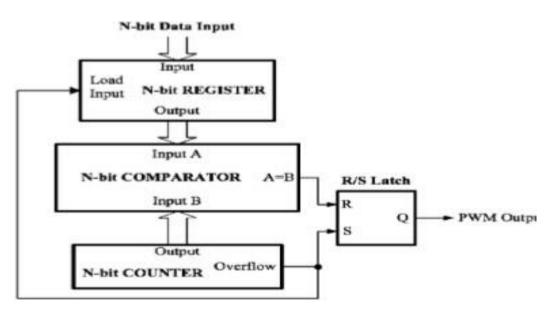

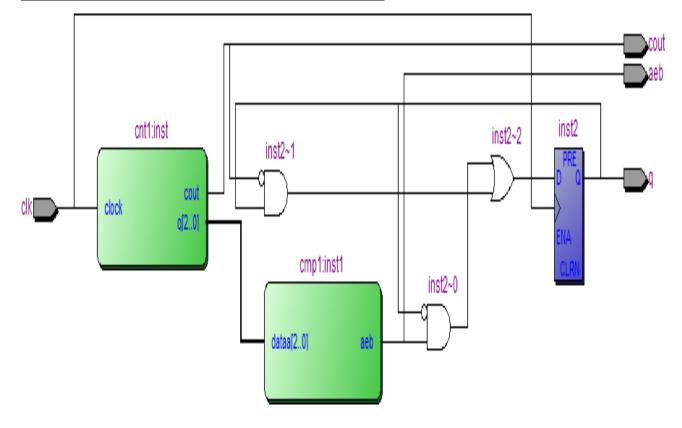

The system input is an N-bit data word, corresponding to the desired PWM duty cycle value. The register stores the input to be processed. So when load input signal is '1' theregister provides input to output. The counter used is 8 bit up- counter. The N-bit register output containing the N-bit data input is compared with the output value of an N-bit counter by means of a comparator. When these two values become equal the comparator output is used to reset the R/S latch output which produces the PWMwave. The R/S latch output is set when the counter reaches an overflow condition at the end of a PWM period. Also the counter overflow signal is used to load the N-bit data input to the input register. R/S latch is used to set or reset the output. When 'r' signal is '1' output is reset to '0'. When 's' signal is '1' output is set to '1'. The duty cycle of the PWM signal is controlled by the data value. The higher the data value the higher the duty cycle.

Experimental Set up :

Switches X10 LEDs X10 Push-buttons

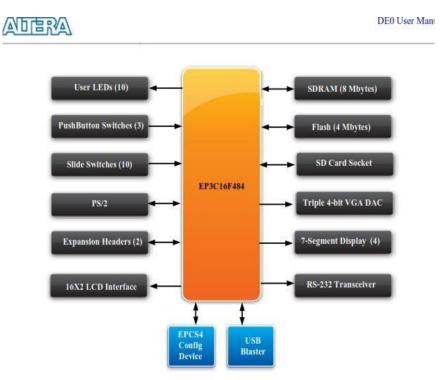

## Fig: DE0 Board

DC Motor :

Fig: Brushless DC Motor

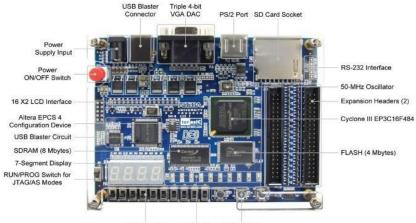

The following hardware is provided on the DE0 board:

- Altera Cyclone, III 3C16 FPGA device

- Altera Serial Configuration device EPCS4

- USB Blaster (on board) for programming and user API control; bothJTAG

and Active Serial (AS) programming modes are supported

- 8-Mbyte SDRAM

- 4-Mbyte Flash memory

- SD Card socket

- 3 pushbutton switches

- 10 toggle switches

- 10 green user LEDs

- 50-MHz oscillator for clock sources

- VGA DAC (4-bit resistor network) with VGA-out connector

- RS-232 transceiver

- PS/2 mouse/keyboard connector

- Two 40-pin Expansion Headers

Fig: Cyclone IIII 3C16 FPGA

- □ 15,408 LEs

- □ 56 M9K Embedded Memory Blocks

- □ 504K total RAM bits

- $\Box$  56 embedded multipliers

- $\Box$  4 PLLs

- $\Box$  346 user I/O pins

- □ FineLine BGA 484-pin package

## **Built-in USB Blaster circuit:**

On-board USB Blaster for programming and user API (Application programminginterface) control

Using the Altera EPM240 CPLD

## **SDRAM**

One 8-Mbyte Single Data Rate Synchronous Dynamic RAM memory chip

Supports 16-bits data bus

#### Flash memory (4-Mbyte NOR Flash memory)

□ Support Byte (8-bits)/Word (16-bits) mode

## SD card socket to Provide both SPI and SD 1-bit mod SD Card access

#### **Pushbutton switches**

$\Box$  3 pushbutton switches

□ Normally high; generates one active-low pulse when the switch is pressed

#### **Slide switches**

$\Box$  10 Slide switches

$\Box$  A switch causes logic 0 when in the DOWN position and logic 1 when in the UP position

#### **General User Interfaces**

- □ 10 Green color LEDs (Active high)

- $\Box$  4 seven-segment displays (Active low)

□ 16x2 LCD Interface (Not include LCD module)

#### **Clock inputs - 50-MHz oscillator**

## **VGA** output

- Uses a 4-bit resistor-network DAC

- □ With 15-pin high-density D-sub connector

□ Supports up to 1280x1024 at 60-Hz refresh rate

#### Serial ports

□ One RS-232 port (Without DB-9 serial connector)

$\Box$  One PS/2 port (Can be used through a PS/2 Y Cable to allow you to connect akeyboard and mouse to one port)

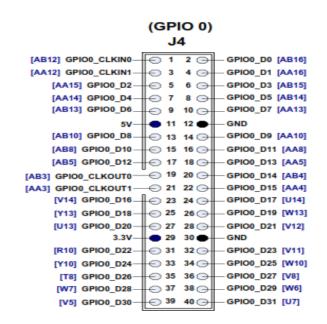

#### **Two 40-pin expansion headers**

□ 72 Cyclone III I/O pins, as well as 8 power and ground lines, are brought out to two40-pin expansion connectors

$\Box$  40-pin header is designed to accept a standard 40-pin ribbon cable used for IDE hard drives

#### **Expansion Header :**

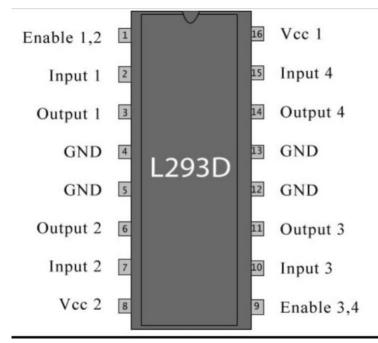

## **L293D Motor driver:**

The 1293d is a 16 pin IC, with eight pins, on each side, dedicated to the controlling of a motor. There are 2 INPUT pins, 2 OUTPUT pins, and one ENABLE pin for each motor. L293d consists of two H-bridge H-bridge is the simplest circuit for controlling a low current rated motor.

Fig: L293D Motor Driver IC

## **Pin characteristics:**

- Enable 1,2 when this is HIGH the left part of the IC will work and whenit is low the left part won't work. So, this is the master control pin for the the part of IC.

- INPUT 1, when this pin is HIGH the current will flow through OUTPUT 1.

- OUTPUT 1, this pin should be connected to one of the terminal of motor.

- GND, ground pins.

- OUTPUT 2, this pin should be connected to one of the terminal of motor.

- INPUT 2, when this pin is HIGH the current will flow through output 2.

- VC, this is the voltage will be supplied to the motor. So, if you aredriving 12 v DC motors then make sure that this pin is supplied with 12v

- VSS, this is the power source to the IC. So, this pin should be supplied with 5v.

- INPUT 4, when this pin is HIGH the current will flow through output 4.

- OUTPUT 4, this pin should be connected to one of the terminal of motor.

- GND, ground pins.

- OUTPUT 3, this pin should be connected to one of the terminal ofmotor.

- INPUT 3, when this pin is HIGH the current will flow through output 3.

- ENABLE 3-4, when this is high the right part of the IC will work and when it is low the right part won't work.so, this is the master control pin for the right part of IC.

## Schematic of the PWM Circuit in Quartus – II IDE :

Simulation Result : – Pulse Width Modulation Waveform

| <b>\$</b> 1• | Msgs    |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

|--------------|---------|----|---------|--------|-----|------|----------|---------|-----|------|---------|------|------|-------|---------|

| /pwm/q       | 0       |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

| /pwm/dk      | 1       |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

|              | 0       |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

| /pwm/aeb     | 1       |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

|              |         |    |         |        |     |      |          |         |     |      |         |      |      |       |         |

| Now Now      | 2600 ps | 35 | r tra a | 500 ps | 100 | 0 ps | e la com | 1500 ps | 200 | 0 ps | 2500 ps | 3000 | ) ps | 1.1.1 | 3500 ps |

#### **Conclusion:**

The PWM output got from the circuit drawn using Schematic in Quartus – II IDE was simulated. The functionality is verified. This output is fed to the motor through the motor driver and thus the speed of the input is changed. This work can be extended for the MPPT controller to extract maximum power from the Solar PV panels by adjusting the firing angle in the DC - DC converter used in MPPT.

#### REFERENCES

- [1] N. Mohan, T. Undeland, W. Robbins, Power Electronics: Converters, Applications and Design, second ed., Wiley, 1995.

- [2] R. Miftakhutdinov, A. Nemchinov, V. Meleshin, S. Fraidlin, Modified Asymmetrical ZVS half-bridge DC– DC converter, in: Proc. Applied Power Electronics Conference and Exposition, vol. 1, 1999, pp. 567–574.

- [3] J. Cheng, A. Witulski, J. Vollin, A small-signal model utilizing amplitude modulation for the Class-D converter at fixed frequency, IEEE Transactions on Power Electronics 15 (2000) 1204–1211.

- [4] K. Arshak, B. Almukhtar, The design and development of anovel flyback planar transformer for high frequency switch mode DC–DC converter applications, Microelectronics Journal 31 (2000) 929–935.

- [5] P. Dananjayan, V. SriRam, C. Chellamuthu, A flyback constant frequency ZCS–ZVS quasi-resonant converter, Microelectronics Journal 29 (1998) 495–504.

- [6] T. Gupta, R.R. Boudreaux, R.M. Nelms, J.Y. Hung, Implementation of a fuzzy controller for DC–DC converters using an Inexpensive 8-b microcontroller, IEEE Transactions on Industrial Electronics 44 (1997) 661–669.

- [7] E. Koutroulis, K. Kalaitzakis, N.C. Voulgaris, Development of a microcontroller-based photovoltaic maximum power point tracking control system, IEEE Transactions on Power Electronics 16 (2001) 46–54.

- [8] C. Hua, J. Lin, C. Shen, Implementation of a DSP controlled photovoltaic system with peak powertracking, IEEE Transactions on Industrial Electronics 45 (1998) 99–107.

- [9] A. Dancy, R. Amirtharajah, A. Chandrakasan, High efficiency multiple-output DC–DC conversion for lowvoltage systems, IEEE Transactions on Very Large Scale Integration (VLSI) Systems 8 (2000) 252–263.

- [10] A. Peterchev, J. Xiao, S. Sanders, Architecture and IC implementation of a digital VRM controller, IEEE Transactions on Power Electronics 18 (2003) 356–364.

- [11] B. Patella, A. Prodic´, A. Zirger, D. Maksimovic´, High frequency digital PWM controller IC for DC–DC converters, IEEE Transactions on Power Electronics 18 (2003) 438–446.

- [12] R. Ramos, X. Roset, A. Manuel, Implementation of fuzzy logic controller for DC/DC converters using field programmable gate array, in: Proc. 17th IEEE Instrumentation and Measurement Technology Conference, vol. 1, 2000, pp. 160–163.

- [13] T. Ide, T. Yokoyama, A study of deadbeat control for three phase PWM inverter using FPGA based hardware controller, in: Proc. IEEE 35th Annual Power Electronics Specialists Conference, vol. 1, 2004, pp. 50–53.

- [14] R. Ruelland, G. Gateau, T. Meynard, J. Hapiot, Design of FPGA-based emulator for series multicell converters using co-simulation tools, IEEE Transactions on Power Electronics 18 (2003) 455–463.

- [15] A.M. Omar, N. Rahim, S. Mekhilef, Three-phase synchronous PWM for flyback converter with power- factor E. Koutroulis et al. / Journal of Systems Architecture 52 (2006) 332–344 343 correction using FPGA ASIC design, IEEE Transactions on Industrial Electronics 51 (2004) 96–106.

- [16] R. Ramos, D. Biel, E. Fossas, F. Guinjoan, A fixed frequency quasi-sliding control algorithm: application to power inverters design by means of FPGA implementation, IEEE Transactions on Power Electronics 18 (2003) 344–355.

- [17] S. Jung, M. Chang, J. Jyang, L. Yeh, Y. Tzou, Design and implementation of an FPGAbased control IC for Ac voltage regulation, IEEE Transactions on Power Electronics 14 (1999) 522–532.

- [18] A. Arbit, D. Pritzker, A. Kuperman, R. Rabinovici, A DSP controlled PWM generator using fieldprogrammable gate array, in: Proc. 23rd IEEE Convention of Electrical and Electronic Engineers, vol. 1,2004, pp. 325–328.

- [19] M.M. Islam, D. Allee, S. Konasani, A. Rodriguez, A lowcost digital controller for a switching DC converter with improved voltage regulation, IEEE Power Electronics Letters 2 (2004) 121–124.

- [20] O. Cadenas, G. Megson, A clocking technique for FPGA pipelined designs, Journal of Systems Architecture 50(2004) 687–696.